CANopen chip F40

-

1. Functional Overview

The CANopen Chip is an insert-ready, highly cost-effective single board computer subassembly with latest CANopen firmware pre-programmed. A simple and cost effective DIP40 connector forms the interface to the target peripherals and transforms the CANopen chip into a versatile utilizable communications interface.

Up to seven IO configurations provide a proper variation of digital inputs and outputs, analog inputs as well as PWM outputs. The on-board hardware configuration units allow the module configuration on deployment time.

The CANopen ChipF40 implements a CANopen slave device according CANopen device profile 401 and CANopen communication profile 301 V4.02. Two LED indicate the device state according to 303-3 V1.0.

2. Properties at a glance

Communication profile according to CiA standard 301 in version V4.02;

Device profile according to CiA standard DSP401;

State indicators according to CiA standard 303-3 V1.0;

Layer Setting Service (LSS) according to CiA standard DSP305;

4 TPDO and 4 RPDO;

Dynamic PDO-Linking and -Mapping;

2 SDO-Server;

Life guarding, Node guarding, Heartbeat;

5 Heartbeat Consumers;

Emergency Producer;

Minimum Boot Up capability;

Manufacturer extension for usage as NMT-boot master.

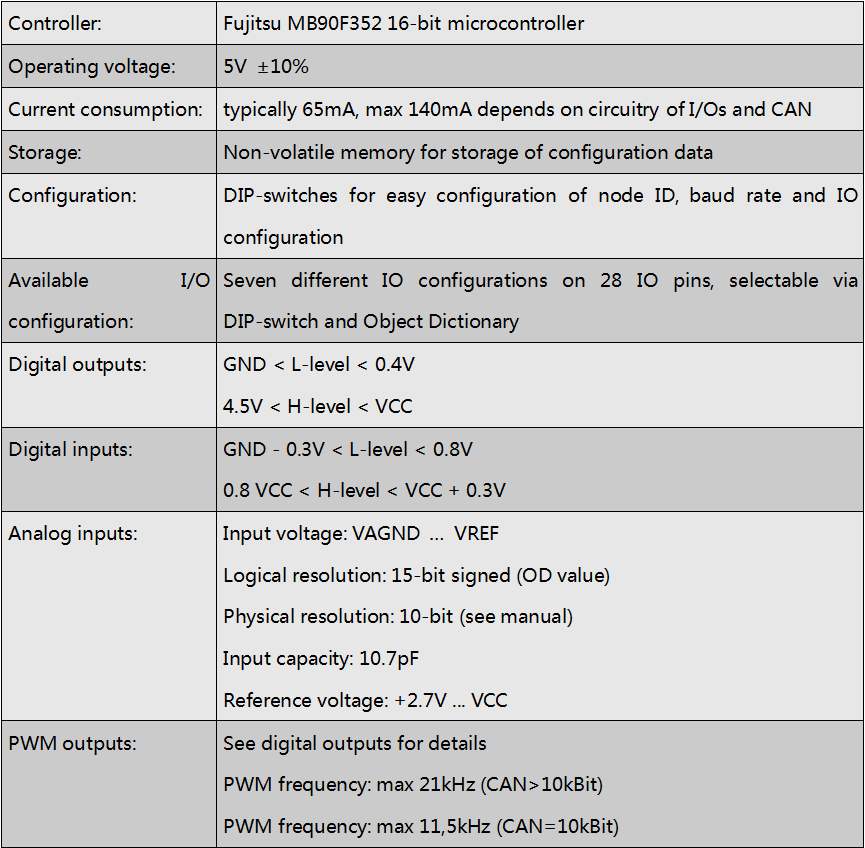

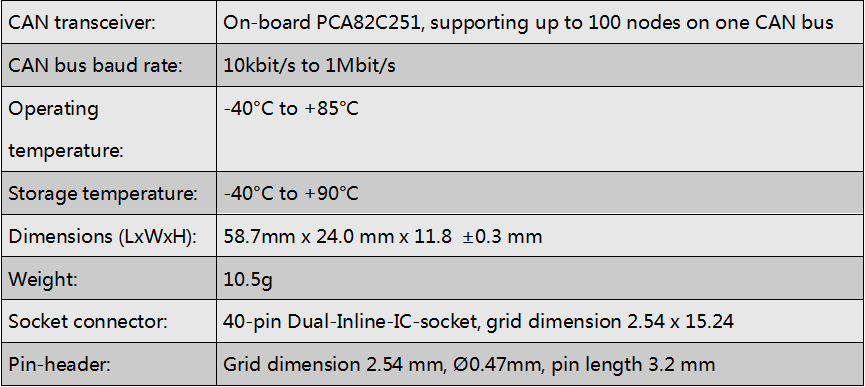

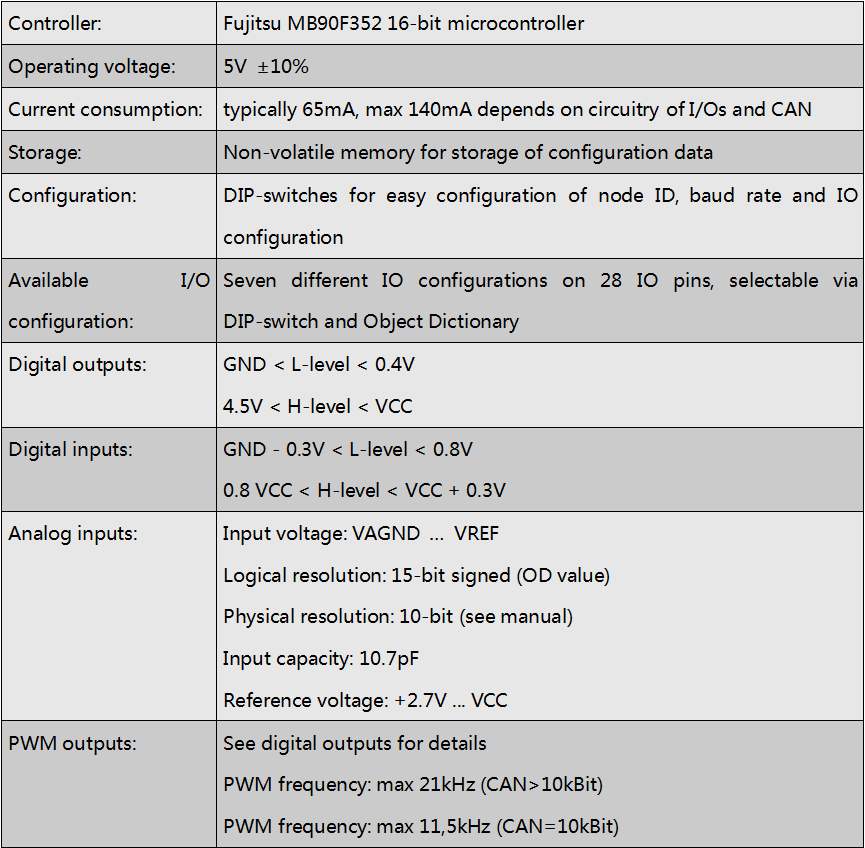

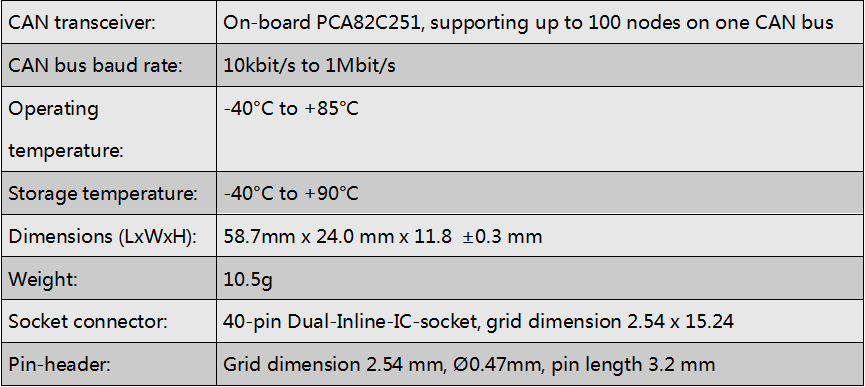

3. Technical specifications

- Communication profile according to CiA standard 301 in version V4.02;

Device profile according to CiA standard DSP401;

State indicators according to CiA standard 303-3 V1.0;

Layer Setting Service (LSS) according to CiA standard DSP305;

4 TPDO and 4 RPDO;

Dynamic PDO-Linking and -Mapping;

2 SDO-Server;

Life guarding, Node guarding, Heartbeat;

5 Heartbeat Consumers;

Emergency Producer;

Minimum Boot Up capability;

Manufacturer extension for usage as NMT-boot master.

-

1. CANopen chipF40 development kit instructions

(Click to view)

2. CANopen chipF40 system manual

(Click to view)

3. CANopen chipF40 user manual(Click to view)